kategória: Najlepšie články » Praktická elektronika

Počet zobrazení: 12919

Komentáre k článku: 0

Čip 4046 (K564GG1) pre zariadenia s rezonančnou retenciou - princíp činnosti

Pri vytváraní výkonového elektronického zariadenia s rezonančnou retenciou v LC obvode je rezonančný riadiaci obvod navrhnutý tak, aby synchronizoval prijaté oscilácie s riadiacimi impulzmi prichádzajúcimi od vodiča.

Úlohou tohto ovládača je udržiavať rezonančné kmity v obvode LC tak, že ho budia včas vlastnými kmitaniami. Aby sa to dosiahlo, musí riadiaca jednotka prijať signál zo slučky z obvodu obsahujúceho údaje o aktuálnej frekvencii a fáze voľných kmitov v nej, a potom, v závislosti od týchto údajov, udržiavať fázu vodiča v synchronizácii s touto frekvenciou a fázou, potom rezonanciou v okruhu sa automaticky uloží.

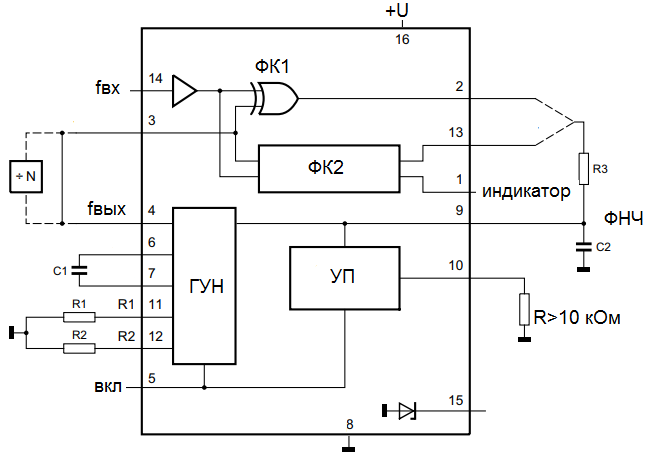

Na zostavenie takéhoto kontroléra je vhodný čip CD4046 alebo jeho domáci náprotivok K564GG1. Pozrime sa na zariadenie tohto mikroobvodu, účel jeho záverov a schému zapojenia namontovaných komponentov, aby sme v prípade potreby porozumeli tomu, čo riešite.

Tento čip vám umožňuje ľahko usporiadať slučku PLL - fázovo uzamknutá. Na zostavenie PLL sa používajú tri potrebné bloky, ktoré sú umiestnené vo vnútri mikroobvodu: VCO - napäťovo riadený oscilátor, FC - fázový porovnávač a LPF - dolnopriepustný filter.

Zabudovaný do mikroobvodu VCO generuje postupnosť pravouhlých impulzov s 50% pokrytím, to znamená čistý meander, ktorého počiatočná frekvencia závisí od parametrov dvoch RC obvodov: R1C1 a R2C2 sú pripojené k nemu mimo mikroobvodu a amplitúda je v tomto prípade blízka napájaciemu napätiu mikroobvodu. U +.

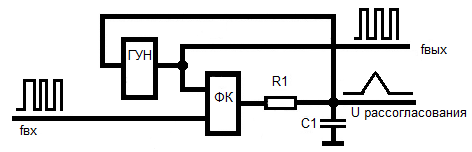

Princíp činnosti PLL

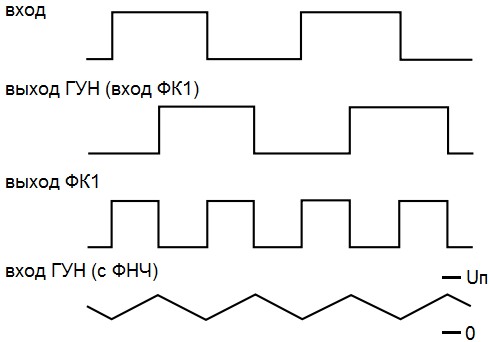

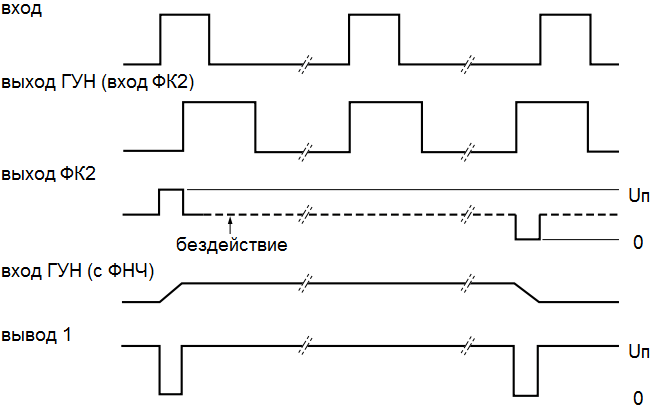

Vonkajší vstupný signál fin je privádzaný do mikroobvodu, v skutočnosti, do jedného zo vstupov fázového porovnávača FC (FC1 alebo FC2 - vývojár vyberie) vo vnútri. Meander produkovaný VCO sa súčasne privádza na druhý vstup FC. V dôsledku toho sa na výstupe FC získa obdĺžnikový signál, ktorého trvanie impulzu závisí od rozdielu medzi impulzmi z VCO a externými impulzmi v každom časovom okamihu.

V skutočnosti je doba trvania výstupných impulzov s FC úmerná fázovému rozdielu dvoch porovnávaných signálov. Faktom je, že výhradný logický prvok OR sa často používa ako FC, to znamená, že na výstupe FC bude vysoká úroveň napätia iba vtedy, ak bude existovať rozdiel medzi signálmi, a ak nebude žiadny rozdiel, potom bude výstup z FC nízky. úroveň napätia alebo neaktívny stav.

Z výstupu FC sa signál privádza do dolnopriepustného filtra, ktorý je jednoduchým RC obvodom, na ktorého kondenzátore sa získava pulzujúce nesúladné napätie, pričom úroveň zvlnenia je úmerná rozdielu medzi dvoma signálmi (z vnútorného VCO a privádzaná do mikroobvodu z vonkajšej strany) - fázový rozdiel ,

Nesprávne napätie získané na kondenzátore LPF sa okamžite privádza späť na vstup VCO a v závislosti od jeho priemernej hodnoty sa frekvencia VCO automaticky naladí tak, aby sa frekvencia meandra na jeho výstupnom výstupe priblížila k frekvencii externého signálu prichádzajúceho z vonkajšej strany mikroobvodu. Po dosiahnutí tejto situácie bude priemerné napätie na kondenzátore dolnopriepustného filtra najmenšie - to je znak začiatku maximálnej konvergencie dvoch signálov vo frekvencii a fáze. Keď je teda signál zachytený, bude ho naďalej držať PLL slučka.

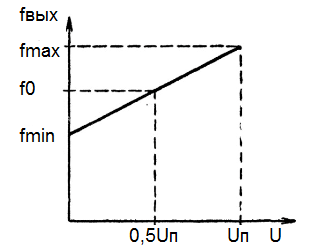

Limity reorganizácie VCO

Ako ste už pochopili, frekvencia VCO je schopná ladiť v rámci určitého rozsahu automatického ladenia. Tento rozsah je nastavený vonkajšími komponentmi čipu. Rýchlosť reakcie systému PLL je určená časovou konštantou LFF (hodnoty C2 a R3).Z tohto dôvodu by ste sa mali prísne zaoberať výberom namontovaných komponentov čipu.

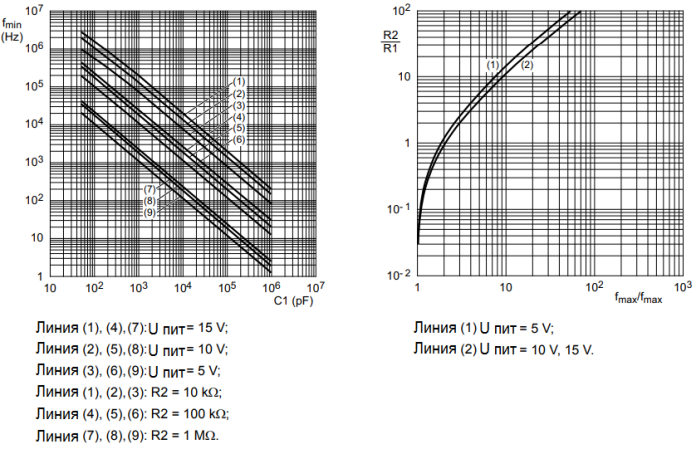

Napájacie napätie mikroobvodu, kondenzátora Cl, ako aj rezistorov R1 a R2 určujú rozsah samokontrolácie frekvencie VCO vo vnútri mikroobvodov. Rezistor R2 ovplyvňuje minimálnu frekvenciu fmin VCO nad nulou. A pomer medzi hodnotami odporov R1 a R2 určuje pomer medzi maximálnou a minimálnou frekvenciou - fmax / fmin, laditeľný výstupný signál z VCO.

Čipové vstupy a výstupy

Záver 4 - výstup signálu VCO, na ňom v pracovnom režime meander. Tento výstup sa môže použiť na dodanie signálu do ďalších blokov navrhovaného zariadenia.

Pin 5 je zodpovedný za zapnutie a vypnutie VCO. Ak je na tento výstup privedené vysoké napätie, mikroobvod sa vypne. Pri použití nízkeho napätia (pri pripájaní kolíka 5 na spoločný vodič) - mikroobvod bude fungovať v normálnom režime.

Závery 6 a 7. K nim je pripojený kondenzátor C1 - to je kondenzátor nastavujúci frekvenciu VCO.

Záver 8 - spoločný napájací drôt čipu.

Rezistor R1 je medzi svorkou 11 a spoločným vodičom. Rezistor R2 - medzi svorkou 12 a spoločným vodičom. Jedná sa o odpory na nastavenie frekvencie. Rezistor R3 dolnopriepustného filtra - na kolík 9 a kolíky 2 alebo 13 (rozdiel medzi nimi bude popísaný neskôr), kondenzátor C2 dolnopriepustného filtra je medzi kolíkom 9 a spoločným vodičom.

Pin 10 je výstupom zosilňovača zosilňovača. Napätie na ňom počas prevádzky mikroobvodu je nesúladné napätie privádzané do dolnopriepustného filtra. Záver 10 je navrhnutý tak, aby sa nezhodné napätie mohlo v prípade potreby ľahko izolovať bez posunutia kondenzátora LPF. Na tento účel je dovolené pripojiť odpor s odporom viac ako 10 kOhm.

Záver 15 - je to katóda zabudovanej zenerovej diódy so stabilizačným napätím 5,6 V (stabilizačné napätie tejto zenerovej diódy sa môže líšiť v závislosti od výrobcu čipu). Táto zenerova dióda sa môže prípadne použiť v napájacom obvode čipu.

Záver 16 - plus sila čipu.

Vstupy a výstupy fázových komparátorov FC1 a FC2

Meander z výstupu VCO je odvedený z terminálu 4 a privedený na terminál 3, pripojený cez zosilňovač-shaper k vstupom fázového porovnávača FC1 a FC2. Ak je to potrebné, signál z VCO môže byť prípadne prepustený cez delič frekvencie.

Vstup 14 je signálový vstup a vstupuje sa do neho vstupný signál, s ktorým je potrebné synchronizovať výstupný signál na výstupe VCO. V závislosti na povahe vstupného signálu si vývojár môže zvoliť, ktorý z fázových komparátorov použiť: FC1 alebo FC2, a k vybratému porovnávači pripojiť rezistor dolného priechodu filtra (na kolík 2 alebo 13). Fázový porovnávač FC2 má indikátorový kolík 1, pri maximálnej synchronizácii signálov sa na ňom objaví vysoké napätie.

Zvláštnosťou FC1 je to, že je to jednoduchý exkluzívny logický prvok ALEBO a kvalita jeho činnosti závisí od parametrov dolnopriepustného filtra na jeho výstupe. Práca začína so strednou frekvenciou f0 = (fmax-fmin) / 2, je možné zachytiť harmonické hodnoty stredovej frekvencie. Má vysokú hlučnosť.

Zvláštnosťou FC2 je, že spracováva iba kladné rozdiely v pulzoch, ktoré sa mu dodávajú, a preto nezáleží na pracovnom cykle impulzov. Práca začína na minimálnej frekvencii fmin, nie je možné zachytiť harmonické frekvencie centrálnej frekvencie. Má nízku hlučnosť. V dolnopriepustnom filtri je potrebný kondenzátor s nízkym zvodovým prúdom. FC2 je vhodnejší na použitie v silových obvodoch s LC rezonanciou.

Výber príloh

Ako dolnopriepustný filter dolnopriepustného filtra je nainštalovaný odpor R3 a kondenzátor C2. Aby PLL správne fungovala, časová konštanta RC musí byť desaťkrát väčšia ako približná frekvencia snímania PLL.

Frekvencia snímania je pre vývojárov spravidla približne známa, preto sú spočiatku nastavené v rozsahu automatického ladenia frekvencie: fmin a fmax. Prvý nomogram určuje hodnoty R2 a C1, berúc do úvahy napájacie napätie mikroobvodu a požadované fmin.Potom sa podľa druhého nomogramu na základe požadovaného pomeru fmax / fmin vyberie R1. Je lepšie poskytnúť schopnosť nastaviť odpory v obvode.

Pozri tiež na electro-sk.tomathouse.com

: